(差异) ←上一版本 | 最后版本 (差异) | 下一版本→ (差异)

这一节介绍指令执行过程中的访问时序。AVR CPU 由系统时钟clkCPU 驱动。此时钟直接来自选定的时钟源。芯片内部不对此时钟进行分频。

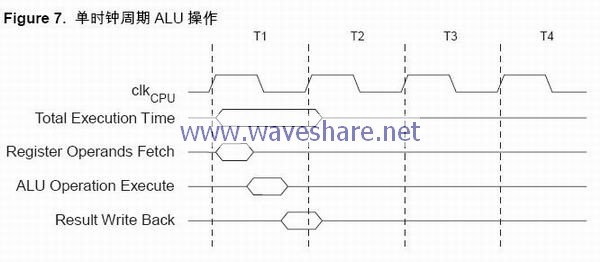

Figure 6 说明了由Harvard 结构决定的并行取指和指令执行,以及可以进行快速访问的寄存器文件的概念。这是一个基本的流水线概念,性能高达1 MIPS/MHz,具有优良的性价比、功能/ 时钟比、功能/ 功耗比。

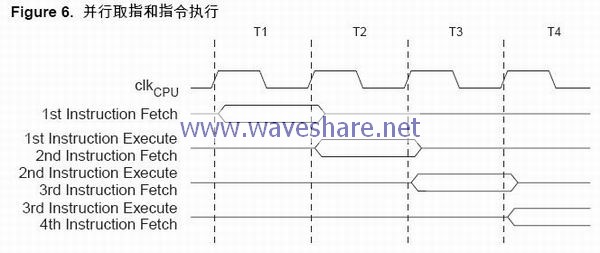

Figure 7 演示的是寄存器文件内部访问时序。在一个时钟周期里,ALU 可以同时对两个寄存器操作数进行操作,同时将结果保存到目的寄存器中去。

Figure 7 演示的是寄存器文件内部访问时序。在一个时钟周期里,ALU 可以同时对两个寄存器操作数进行操作,同时将结果保存到目的寄存器中去。