在Xilinx ISE下创建编译新工程

来自丢石头百科

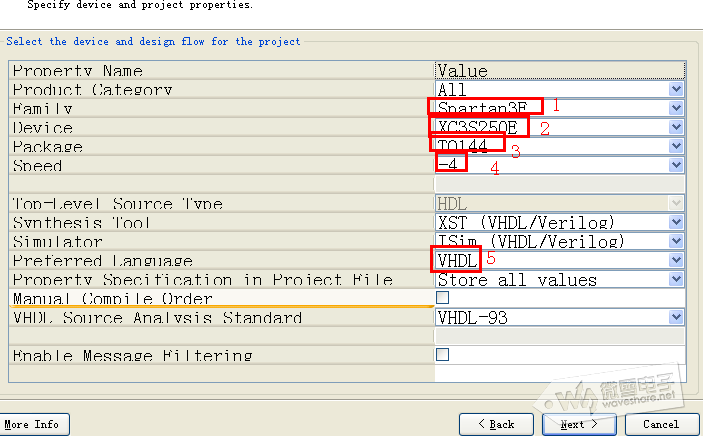

以下配置芯片皆以XC3S250E为例,配置下载器以Platform Cable USB为例,配置时要选对应的芯片型号与下载器

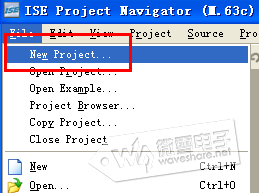

1,点击Xilinx ISE,如下图:

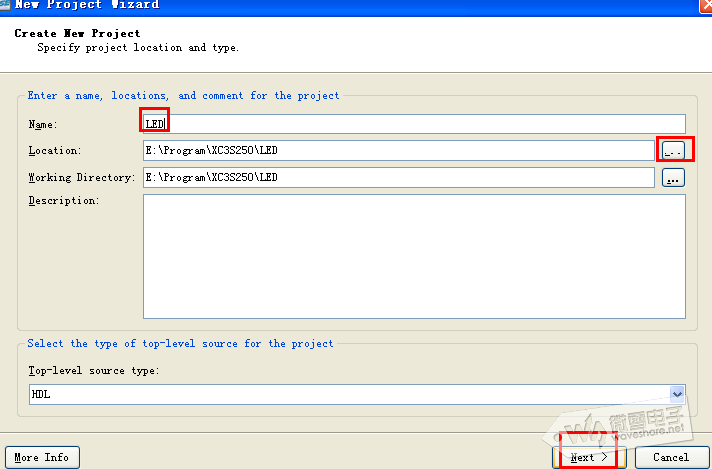

2, 创建工程名并保存到相应文件夹,如下图:

3 ,如下图:

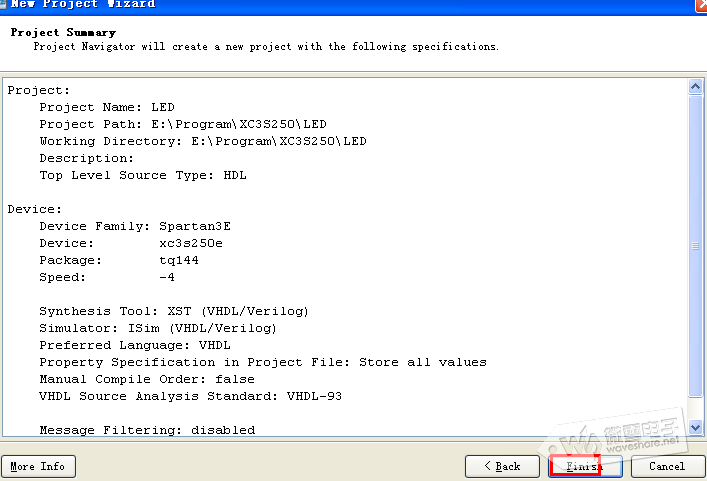

4,如下图:

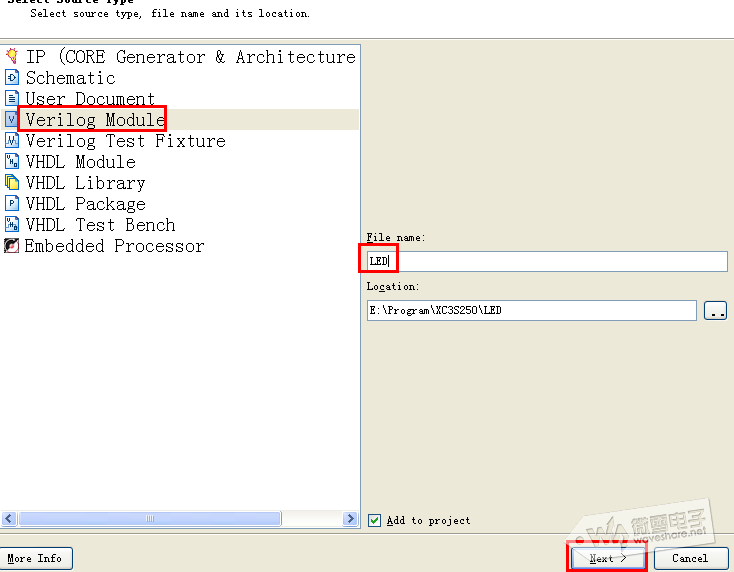

5,添加一个Verilog HDL文件,如下图:

6,如下图:

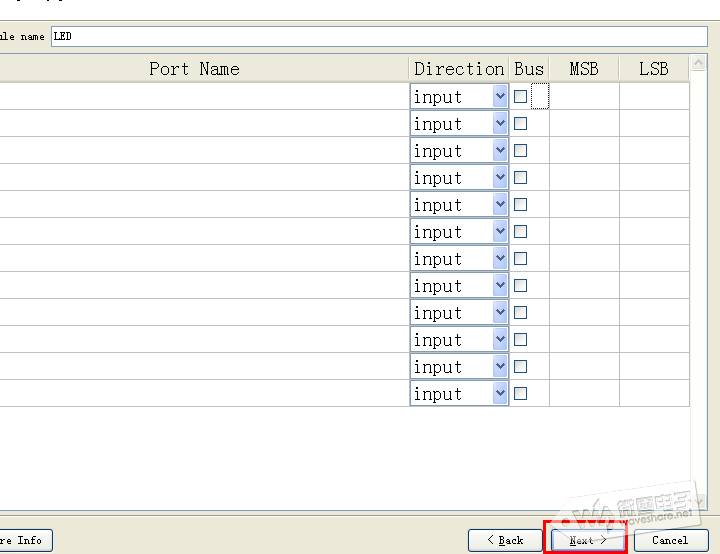

7, 如下图:

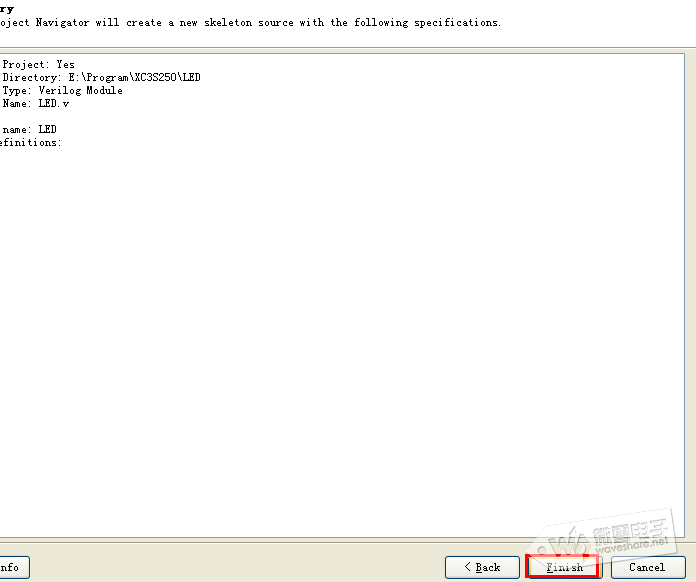

8,如下图:

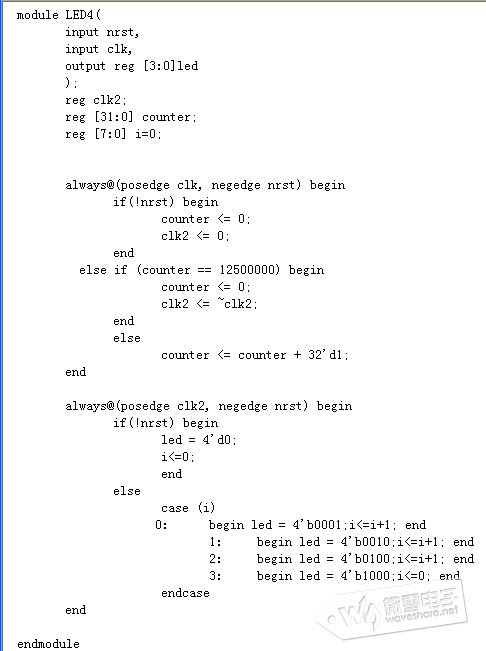

9,Verilog HDL内的代码如下,写完代码后保存:

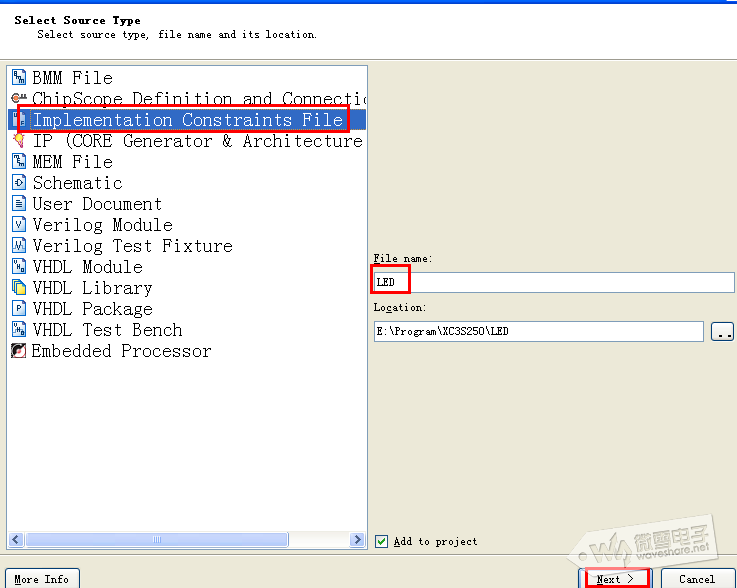

10,创建管脚配置文件,如下图:

11,如下图:

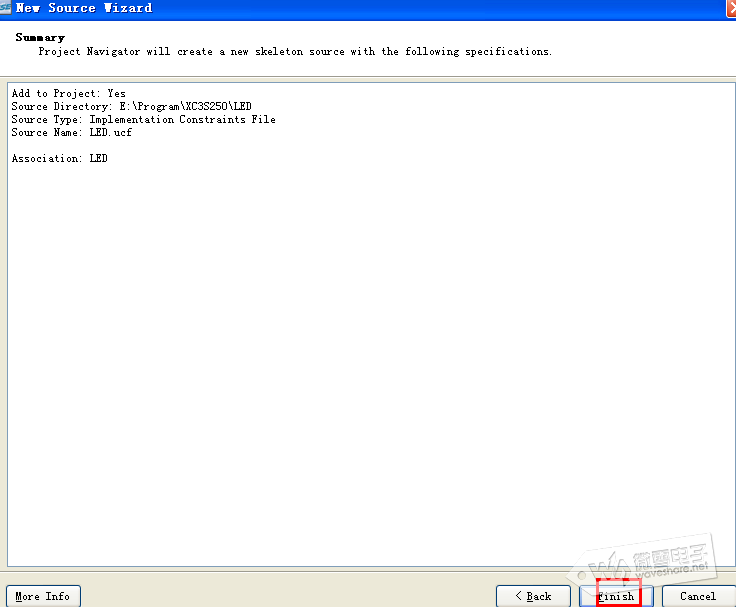

12,如下图:

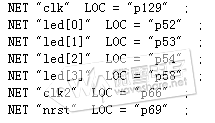

13,管脚配置文件如下:

14,点击如下图标开始编译: